## Code No. 5398 / OTC

# FACULTY OF ENGINEERING

B.E. 4/4 (Civil) I - Semester (One Time Chance) Examination, January 2016

## Subject : Matrix Methods and Numerical Techniques

Max. Marks: 75

(2)

(3)

(2)

(2)

Note: Answer all questions from Part-A and answer any five questions from Part-B.

## PART – A (25 Marks)

- 1 What is the static indeterminacy of single storey, two bay portal frame with hinged bases?

- 2 List out the properties of a stiffness matrix.

- 3 Define the term flexibility.

Time: 3 Hours

- 4 Generate the flexibility matrix for a cantilever corresponding to the flexural deformations of free end. (3)

- 5 What is the reason for symmetry of stiffness matrix?

- 6 Derive the relation between flexibility and stiffness matrices. (3)

- 7 What are equivalent joint loads in case of a fixed beam subjected to u.d.l. over entire span?(2)

- 8 Briefly explain the Gauss-Seidel iteration method. (3)

- 9 How many intervals are present in Simpson's 3/8<sup>th</sup> rule? (2)

- 10 What are the interior points in finite difference method?(3)

## PART – B (50 Marks)

(a) Distinguish between the flexibility and stiffness methods of structural analysis.

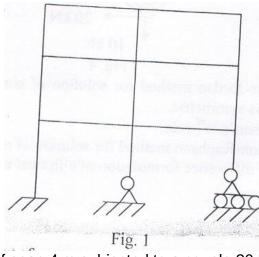

(b) Determine the static and kinematic indeterminacies of the frame shown in figure 1.

12 Analyse a fixed beam of span 4 m subjected to a couple 20 kNm at mid span using flexibility method and draw SFD and BMD. (10)

..2

(5)

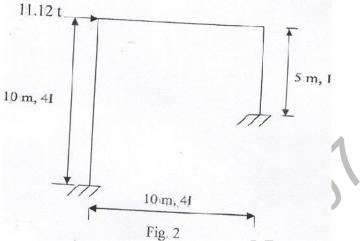

13 Analyse the portal frame shown in figure 2 by flexibility method and draw SFD and BMD. (10)

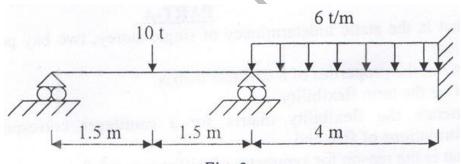

14 Analyse the continuous beam shown in figure 3 by stiffness method and draw SFD and BMD. (10)

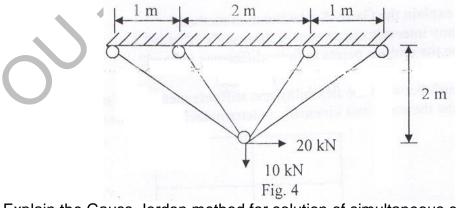

15 Using stiffness method, determine the forces in members of the pin-jointed truss shown in figure 4. Take area of all members as 20 cm<sup>2</sup> and E = 200 GPA. (10)

- 16 (a) Explain the Gauss-Jordon method for solution of simultaneous equation of the type A  $\dot{X}$  = B, when A is symmetric. (b) Explain the Simpson's 1/3<sup>rd</sup> rule. (5)

- 17 (a) Explain the Newton-Raphson method for solution of non-linear equations. (5) (b) Explain the finite difference formulation of elliptical equations. (5)

# FACULTY OF ENGINEERING

## B.E. 4/4 (ECE) I – Semester Examination, January 2016

## Subject : Verilog HDL

### Time : 3 hours

# Note: Answer all questions from Part-A. Answer any FIVE questions from Part-B.

## PART – A (25 Marks)

| <ol> <li>Give the syntax for \$ monitor system task.</li> <li>Write the syntax for instantiation of buf / not gates in verilog.</li> <li>Differentiate between regular assignment delay and implicit continuous delay with syntax.</li> <li>What is the significance of sensitive list?</li> <li>Mention the syntax for force and release statements.</li> <li>Give example for concatenation operation.</li> <li>Give the differences between combinational and sequential UDP's.</li> <li>What is logic synthesis?</li> <li>What are the uses of programming language interface?</li> <li>Give the differences between behavioural and dataflow modeling.</li> </ol> | 2<br>3<br>2<br>2<br>2<br>3<br>2<br>3<br>3<br>3<br>3 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| PART – B (50 Marks)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                     |

| <ul><li>11 a) With the help of flow chart, discuss about IC design flow.</li><li>b) Write verilog code for 4 to 1 multiplexer in structural model.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5<br>5                                              |

| <ul><li>12 a) Give differences between blocking and non-blocking assignments with one example for each.</li><li>b) Write verilog code for 8 to 3 priority encoder.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | e<br>5<br>5                                         |

| <ul><li>13 a) Give the differences between tasks and functions.</li><li>b) Write verilog code for 8-bit parallel adder using functions.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4<br>6                                              |

| <ul><li>14 a) Give the differences between Moore and Mealy finite state machines.</li><li>b) Write verilog code for 1011 sequence detector using Moore finite state machine.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3<br>7                                              |

| <ul><li>15 a) Discuss about logic synthesis flow from RTL to gates.</li><li>b) Write verilog code for 4-bit counter in structural model.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4<br>6                                              |

| 16 Write verilog code for 4-bit carry look ahead adder and also write test bench for it.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 10                                                  |

| <ul> <li>17 Write short notes on :</li> <li>a) Conditional compilation and conditional execution</li> <li>b) User defined primitive</li> <li>c) Verilog code for 2 to 1 multiplexer in switch level model.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3<br>4<br>3                                         |

\*\*\*\*\*

## Max. Marks : 75

# FACULTY OF ENGINEERING

## B.E. 4/4 II - Semester (One Time Chance) Examination, January 2016

## **Subject : Production and Operation Management**

#### Time : 3 Hours

Max. Marks: 75

*Note: Answer all questions from Part-A and answer any five questions from Part-B.* PART – A (25 Marks)

- 1 Explain the factors affecting plant layout.

- 2 Define method study and time study.

- 3 Discuss adaptive exponential smoothing method.

- 4 Explain multiple regression.

- 5 Write note on aggregate planning.

- 6 Explain Master Production Scheduling.

- 7 Explain Economic Order Quantity.

- 8 Define (a) Lead time (b) Buffer stock

- 9 Define (a) Total float (b) slack

- 10 Write the applications of CPM and PERT.

## PART – B (50 Marks)

- (a) Explain with neat sketches Product and Process type of plant layout.

(b) The total observed time for an operation in 4 min. If the rating is 120% find normal time. If total allowance allowed is 10% for the job. Compute the standard time.

(4)

- 12 (a) Explain exponential smoothing with trend.

- (b) A firm uses simple exponential smoothing with  $\alpha$ = 0.1to forecast demand. The forecast for the week of June 2016 was 700 units whereas the actual demand turned out to be 650 units. Compute the demand forecast for the week of July, 2016. (6)

## 13 (a) Explain MRP system with its inputs and outputs.

- (b) Discuss in detail about the MRP-II.

- 14 (a) Discuss the costs associated with inventory.(b) Explain ABC analysis.

- 15 Draw the project network, find the critical path, find the probability that the project is completed in 19 days. If the probability is less than 20%, find the probability of completing it in 24 days.

| , it in 24 days. |          |               |    |                          |    |  |  |

|------------------|----------|---------------|----|--------------------------|----|--|--|

|                  | Activity | Activity Name | To | T <sub>m</sub> (in days) | tp |  |  |

|                  | i j      |               |    |                          |    |  |  |

|                  | 1-2      | А             | 4  | 6                        | 8  |  |  |

|                  | 1-3      | В             | 2  | 3                        | 10 |  |  |

|                  | 1-4      | С             | 6  | 8                        | 16 |  |  |

|                  | 2-4      | D             | 1  | 2                        | 3  |  |  |

|                  | 3-4      | E             | 6  | 7                        | 8  |  |  |

|                  | 3-5      | F             | 6  | 7                        | 14 |  |  |

|                  | 4-6      | G             | 3  | 5                        | 7  |  |  |

|                  | 4-7      | Н             | 4  | 11                       | 12 |  |  |

|                  | 5-7      | I             | 2  | 4                        | 6  |  |  |

|                  | 6-7      | J             | 2  | 9                        | 10 |  |  |

\*\*\*\*\*

- 16 Write short notes on the following:(a) Plant location (b) Forecasting error

- 17 Write short notes on the following: (a) Critical path (b) Crash analysis

(4)

(5) (5)

(5)

(5)

# FACULTY OF ENGINEERING

B.E. 3/4 (Inst.) II - Semester (One Time Chance) Examination, January 2016

## Subject : Power Engineering

Max. Marks: 75

1

Note: Answer one question from each unit. All questions carry equal marks.

## Unit – I

1 Draw the complete schematic diagram of a steam power plant. Label each component. Discuss briefly the function of each component.

#### OR

2 (a) Discuss the merits and demerits of hydro-electric plants.(b) How a surge tank helps in reducing the water hammer effect?

## Unit – II

- 3 a) What are the factors to be considered in selecting the site of a nuclear power station?

- b) Explain the following terms with reference to a nuclear reactor:i) moderatorii) coolent

## OR

4 List and explain the factors that influence the economic choice of equipment.

#### Unit – III

5 Name different components of overhead line. Also explain the purpose for which they are used.

#### OR

6 Derive the expression for inductance of transmission line per km per conductor.

## Unit – IV

7 (a) What is meant by regulation of a transmission line? Why its knowledge is essential?(b) What is meant by Ferranti effect? Explain with the help of phasor diagram.

#### OR

- 8 (a) Explain how a faulted power system is can be represented through single line diagrams?

- (b) Why the per-unit system is used in power system analysis? Which of the electrical quantities are chosen as base values?

## Unit – V

9 What is a protective relay? Explain its function in an electrical system. Explain the role of protection in power systems.

#### OR

10 What is the principle of differential relay? Explain their characteristics and limitations.

\*\*\*\*\*

## Time : 3 Hours