#### CHAPTER 9: ASYNCHRONOUS SEQUENTIAL CIRCUITS

### Chapter Objectives

- Sequential circuits that *are not synchronized by a clock* – Asynchronous circuits

*Analysis* of Asynchronous circuits

- Synthesis of Asynchronous circuits

- Hazards that cause incorrect behavior of a circuit

# Asynchronous sequential circuits

#### 3

- Synchronous sequential circuits

- state variables : F/Fs

- controlled by a clock

- operate in *pulse mode*

- Asynchronous sequential circuits

- do not operate in *pulse mode*

- do not use F/Fs to represent state variables

- Changes in state are dependent on whether each of inputs to the circuit has the logic level 0 or 1 at any given time

- <u>To achieve reliable operation</u> (focus on the simplest case)

- the inputs to the circuit must change one at a time

- there must be sufficient time between the changes in input signals to allow the circuit to reach a stable state

- A circuit that adheres to these constraints is said to operate in the fundamental mode

#### Asynchronous behavior

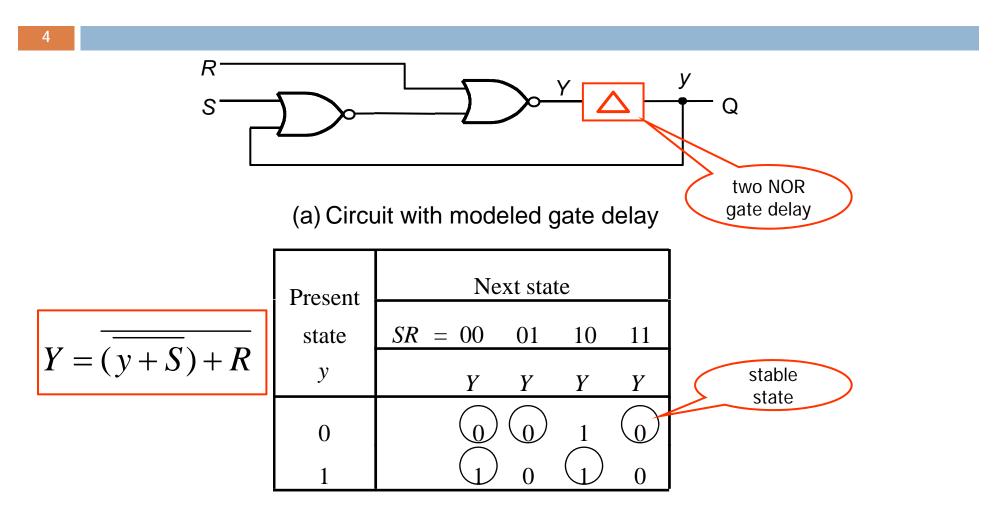

(b) State-assigned table

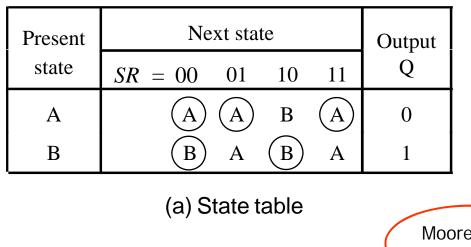

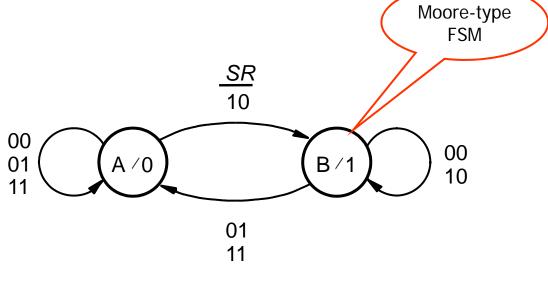

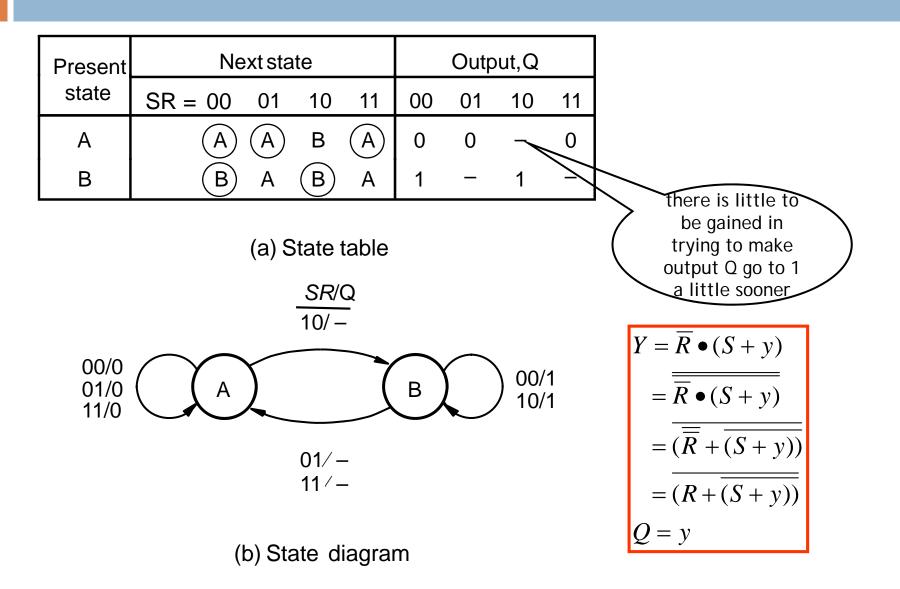

#### FSM model for the SR latch

(b) State diagram

#### Synthesis of an asynchronous circuit

| Present | Nextstate           | Output |

|---------|---------------------|--------|

| state   | SR = 00  01  10  11 | Q      |

| А       | (A) (A) (B) (A)     | 0      |

| В       | B A B A             | 1      |

(a) State table

| Present | Next       | state     |               |            |

|---------|------------|-----------|---------------|------------|

| state   | SR = 00  ( | )1        | 10            | 11         |

| у       | Y          | Y         | Y             | Y          |

| 0       |            | $\hat{0}$ | $\frac{1}{1}$ | $\bigcirc$ |

(b) State-assigned table

$$Y = \overline{R} \bullet (S + y)$$

$$= \overline{\overline{R}} \bullet (S + y)$$

$$= \overline{(\overline{\overline{R}} \bullet (S + y))}$$

$$= \overline{(\overline{\overline{R}} + \overline{(S + y)})}$$

$$= \overline{(R + \overline{(S + y)})}$$

$$z = y$$

#### Mealy representation of the SR latch

7

# Terminology

#### Asynchronous circuits

- state table -> flow table

- state-assigned table -> transition table or excitation table

- We will use the term *flow table and excitation table*

#### Analysis of Asynchronous Circuits

#### Analysis of Asynchronous circuits

#### Analysis of the circuit in example 9.3

# Excitation and flow tables for the circuit in example 9.3

| Present               |                                             | Nextstate                                   |                       |                                             |        |  |  |

|-----------------------|---------------------------------------------|---------------------------------------------|-----------------------|---------------------------------------------|--------|--|--|

| state                 | W2 W1 = 00                                  | 01                                          | 10                    | 11                                          | Output |  |  |

| <i>y</i> 2 <i>y</i> 1 | <b>Y</b> <sub>2</sub> <b>Y</b> <sub>1</sub> | <b>Y</b> <sub>2</sub> <b>Y</b> <sub>1</sub> | <b>Y</b> 2 <b>Y</b> 1 | <b>Y</b> <sub>2</sub> <b>Y</b> <sub>1</sub> | Ζ      |  |  |

| 00                    | 00                                          | 01                                          | 10                    | 11                                          | 0      |  |  |

| 01                    | 11                                          | (01)                                        | 11                    | 11                                          | 0      |  |  |

| 10                    | 00                                          | 10                                          | (10)                  | (10)                                        | 1      |  |  |

| 11                    | (11)                                        | 10                                          | 10                    | 10                                          | 0      |  |  |

(a) Excitation table

| Present | Nex            | Nextstate  |            |            |             |  |

|---------|----------------|------------|------------|------------|-------------|--|

| state   | $W_2 W_1 = 00$ | 01         | 10         | 11         | Output<br>z |  |

| А       | A              | В          | С          | D          | 0           |  |

| В       | D              | B          | D          | D          | 0           |  |

| С       | А              | $\bigcirc$ | $\bigcirc$ | $\bigcirc$ | 1           |  |

| D       | D              | С          | С          | С          | 0           |  |

(b) Flow table

#### Modified flow table for Example 9.3.

13

| Presen | t |           | Output     |            |            |            |   |

|--------|---|-----------|------------|------------|------------|------------|---|

| state  | и | ⁄2 1/11 = | 00         | 01         | 10         | 11         | Z |

| Α      |   |           | (A)        | В          | С          | Ι          | 0 |

| В      |   |           | D          | B          | -          | D          | 0 |

| C      | Í |           | А          | $\bigcirc$ | $\bigcirc$ | <b>(C)</b> | 1 |

| D      |   |           | $\bigcirc$ | С          | С          | С          | 0 |

#### State table for Example 9.3

14

$\begin{array}{c} & & \frac{w_2w_1}{01} \\ 00 \\ & A/0 \\ 10 \\ 10 \\ 10 \\ 10 \\ 10 \\ 00 \\ 11 \\ 00 \\ 11 \\ 00 \\ 11 \\ 00 \\ 11 \\ 00 \\ 11 \\ 00 \\ 00 \\ 11 \\ 00 \\ 00 \\ 11 \\ 00 \\ 00 \\ 11 \\ 00 \\ 00 \\ 11 \\ 00 \\ 00 \\ 11 \\ 00 \\ 00 \\ 00 \\ 11 \\ 00 \\ 00 \\ 00 \\ 11 \\ 00 \\ 00 \\ 00 \\ 11 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 11 \\ 00 \\ 00 \\ 00 \\ 00 \\ 11 \\ 00 \\ 00 \\ 00 \\ 11 \\ 00 \\ 00 \\ 00 \\ 00 \\ 11 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 0$

# Flow table for a simple vending machine

| Present | Nex        | Output     |            |    |   |

|---------|------------|------------|------------|----|---|

| state   | W2 W1 = 00 | 01         | 10         | 11 | Z |

| А       | A          | В          | С          | Ι  | 0 |

| В       | D          | B          | -          | -  | 0 |

| С       | А          | <b>(C)</b> | $\bigcirc$ | -  | 1 |

| D       | D          | С          | С          | -  | 0 |

$W_2 \equiv dime \quad W_1 \equiv nickel$

## Steps in the Analysis Process

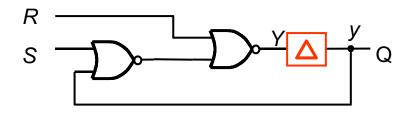

#### Each feedback path is cut

- A delay element is inserted at the point where the cut is made

- A cut can be made anywhere in a particular loop formed by feedback connection, as long as there is only one cut per (state variable) loop

- Next-state and output expressions are derived from the circuit

- The excitation table is derived

- A flow table is obtained

- A corresponding state diagram is derived from the flow table if desired

#### Synthesis of Asynchronous Circuits

#### Synthesis of Asynchronous Circuits

the same basic steps used to synthesize the synchronous circuits

- Devise a state diagram for an FSM

- Derive the flow table and reduce the number of states if possible

- Perform the state assignment and derive the excitation table

- Obtain the next-state and output expressions

- Construct a circuit that implements these expressions

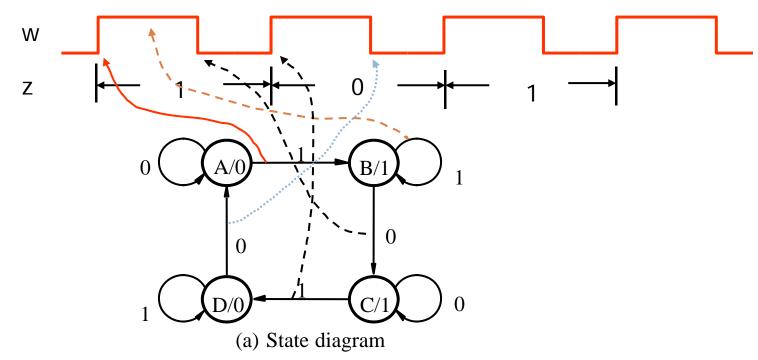

## Example: serial parity generator

- Serial parity generator

- □ input w : pulses are applied to w

- output z

- z=1 if the number of previously applied pulses is odd

#### Parity-generating asynchronous FSM

20

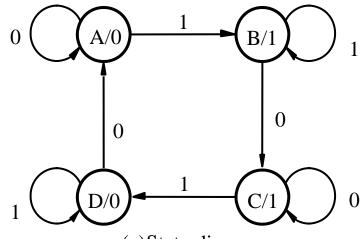

(a)State diagram

| Present | Next       | Output       |     |

|---------|------------|--------------|-----|

| State   | w = 0      | <i>w</i> = 1 | Z I |

| А       | (A)        | В            | 0   |

| В       | C          | B            | 1   |

| C       | $\bigcirc$ | D            | 1   |

| D       | A          | D            | 0   |

#### State assignment

| Present                       | Next  |              |        |

|-------------------------------|-------|--------------|--------|

| state                         | w = 0 | <i>w</i> = 1 | Output |

| y <sub>2</sub> y <sub>1</sub> | Y     | z            |        |

| 00                            | (00)  | 01           | 0      |

| 01                            | 10    | $\bigcirc 1$ | 1      |

| 10                            | (10)  | 11           | 1      |

| 11                            | 00    |              | 0      |

(a) Poor state assignment

| Present                                     | Next  |        |   |

|---------------------------------------------|-------|--------|---|

| state                                       | w = 0 | Output |   |

| <i>y</i> <sub>2</sub> <i>y</i> <sub>1</sub> | Y     | Z      |   |

| 00                                          | (00)  | 01     | 0 |

| 01                                          | 11    | (01)   | 1 |

| 11                                          | (11)  | 10     | 1 |

| 10                                          | 00    | (10)   | 0 |

(b) Good state assignment

- State assignment (a) has a major flaw

- state D =11 : w=0 -> state A

- $y_2y_1 = 11 \rightarrow y_2y_1 = 00$

- the values of the next-state variables determined by the networks of logic gates with varying delays

- suppose y<sub>1</sub> changes first

- y<sub>2</sub>y<sub>1</sub>=10 -> state C(10)

- state C is stable when w=0

- suppose y<sub>2</sub> changes first

- y<sub>2</sub>y<sub>1</sub>=01-> state B (01)

- try to change to y<sub>2</sub>y<sub>1</sub>=10 when w=0

- if y<sub>1</sub> changes first, y<sub>2</sub>y<sub>1</sub>=00

- race condition occurs

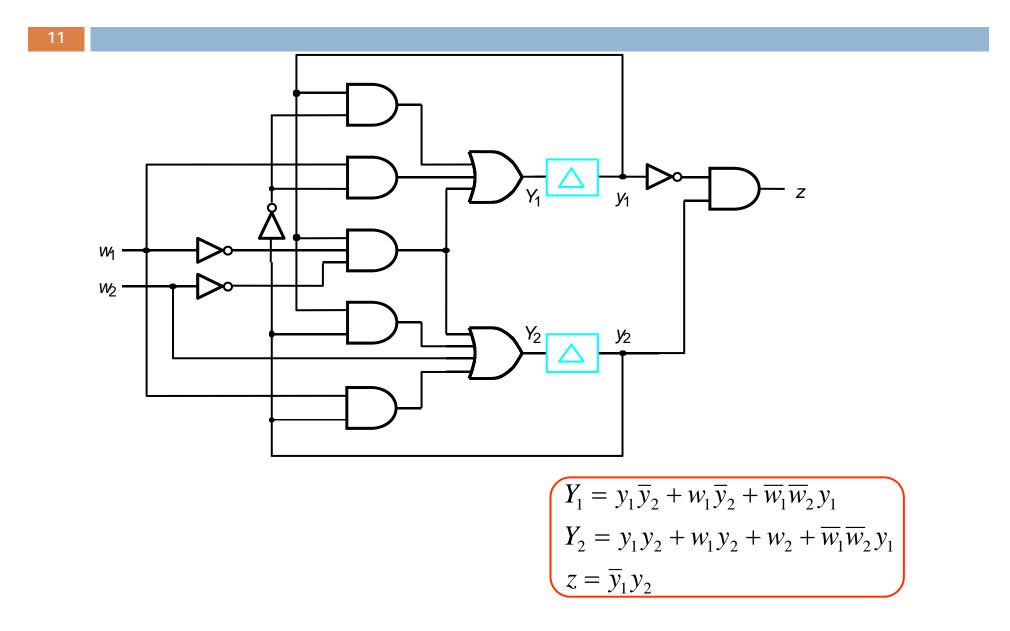

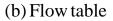

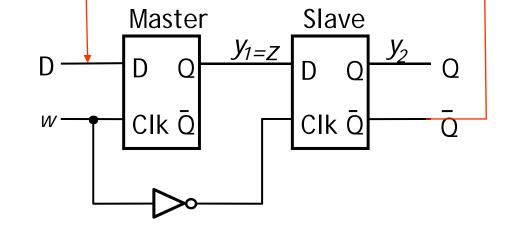

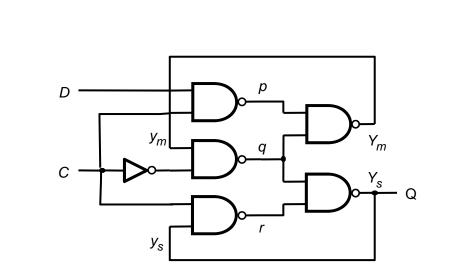

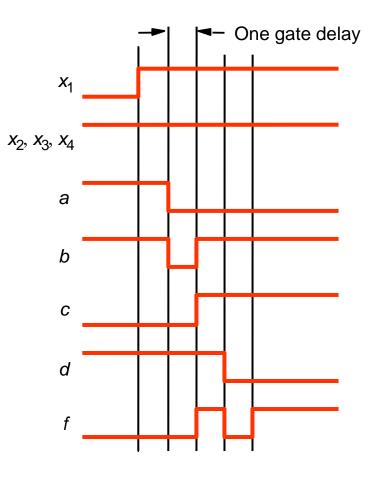

### Circuit that implements the FSM

Circuit that implements a paritygenerating asynchronous FSM

The asynchronous implementation is *more complex* than the synchronous one?

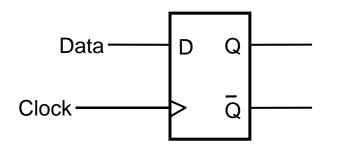

It's a negative-edge-triggered master/slave F/F

With the complement of its output connected to its D input

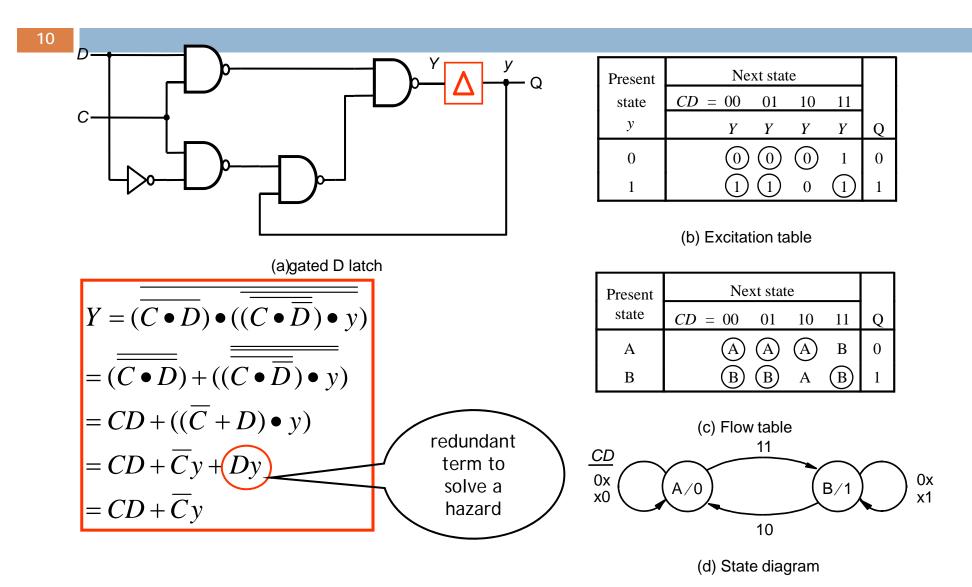

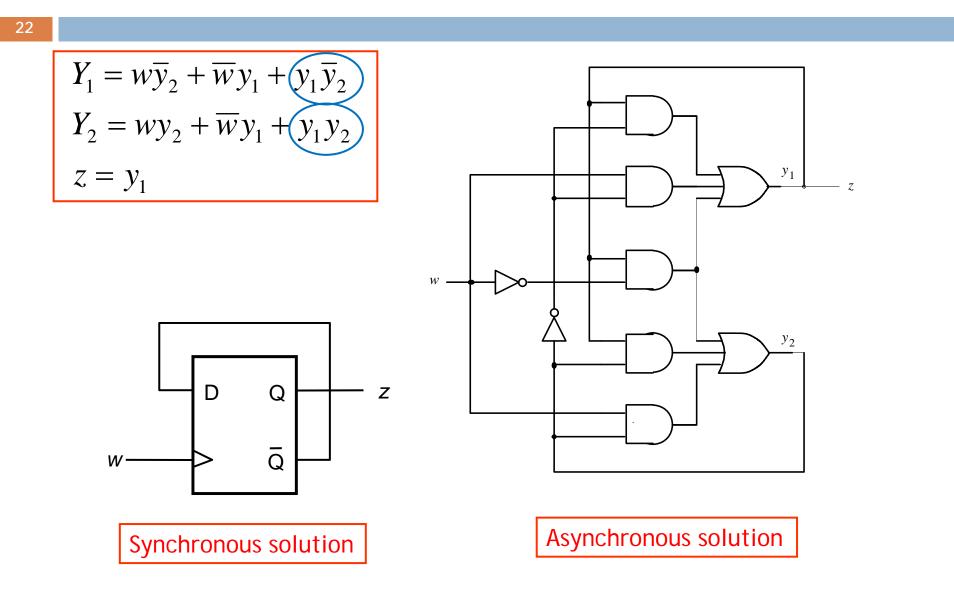

# Master-slave D F/F(example 9.2)

- Analyze synchronous circuit as if it were an asynchronous circuit.

- Actually all circuits are asynchronous

Circuit for the master-slave D flip-flop.

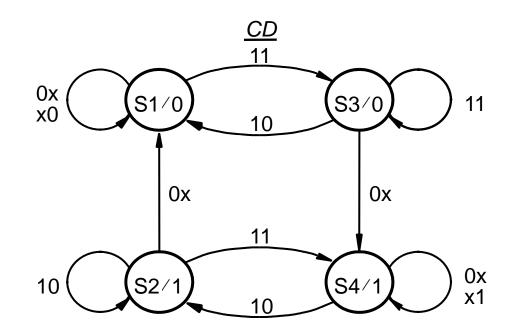

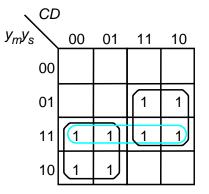

### Excitation table for example 9.2

| Present | Next state              |        |

|---------|-------------------------|--------|

| state   | <i>CD</i> = 00 01 10 11 | Output |

| Ym Ys   | Ym Ys                   | Q      |

| 00      | 00 00 00 10             | 0      |

| 01      | 00 00 01 11             | 1      |

| 10      | 11 11 00 (10)           | 0      |

| 11      | (1) (1) (01 (1))        | 1      |

(a) Excitation table

#### Flow tables for Example 9.2

| Present |    | Next state |     |     |     |             |

|---------|----|------------|-----|-----|-----|-------------|

| state   | CD | = 00       | 01  | 10  | 11  | Output<br>Q |

| S1      |    | \$1        | S1  | \$1 | S3  | 0           |

| S2      |    | S1         | S1  | \$2 | S4  | 1           |

| S3      |    | S4         | S4  | S1  | \$3 | 0           |

| S4      |    | \$4        | \$4 | S2  | \$4 | 1           |

(b) Flow table

| Present |    | Next state |            |     |     |             |

|---------|----|------------|------------|-----|-----|-------------|

| state   | CD | = 00       | 01         | 10  | 11  | Output<br>Q |

| S1      |    | S1         | S1         | \$1 | S3  | 0           |

| S2      |    | S1         | -          | \$2 | S4  | 1           |

| S3      |    | -          | S4         | S1  | \$3 | 0           |

| S4      |    | \$4        | <u>\$4</u> | S2  | \$4 | 1           |

(c) Flow Table with unspecified entries

# State diagram for the master-slave D Flip/Flop

#### Parity generating FSM and Masterslave D F/F

28

$$Y_{1} = w\overline{y}_{2} + \overline{w}y_{1} + y_{1}\overline{y}_{2}$$

$$Y_{2} = wy_{2} + \overline{w}y_{1} + y_{1}y_{2}$$

$$z = y_{1}$$

$Y = CD + \overline{C}y + Dy$

in the previous example

of gated D-Latch

$$Y_m = CD + \overline{C}y_m + Dy_m$$

$$Y_s = \overline{C}y_m + Cy_s + y_m y_s$$

$$y_1 = y_m, y_2 = y_s$$

$$w = C, \overline{y}_2 = D,$$

$$z = y_1 = y_m$$

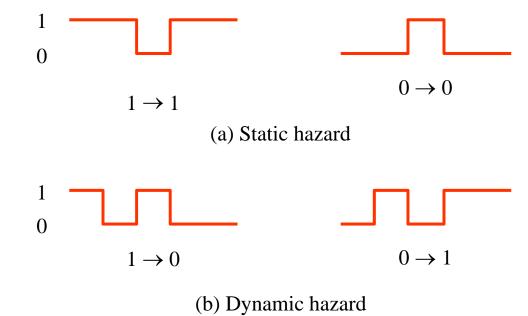

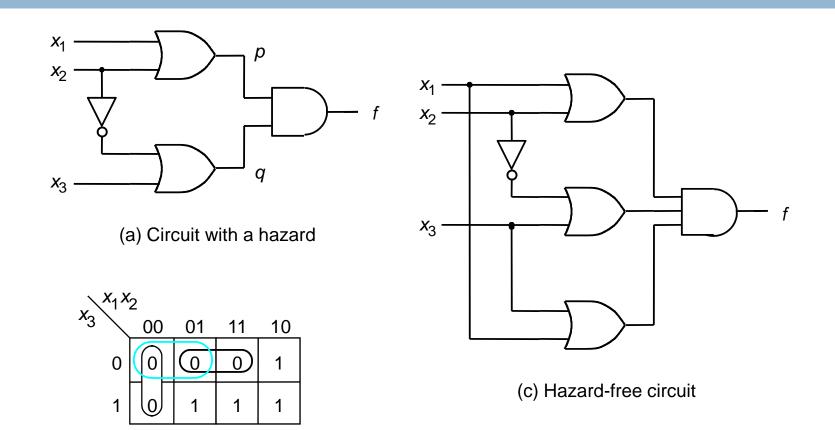

#### **Hazard and Glitches**

## Hazards and glitches

#### 30

- In asynchronous circuits

- undesirable glitches on signals should not occur

- hazards

- the glitches cause by the structure of a given circuit and propagation delays in the circuit

- two types of hazards

- static

- the signal undergoes a momentary change in its required value

- dynamic

- when a signal is supposed to change from 1 to 0 or from 0 to 1

- a change involves a short oscillation before the signal settles into its new level

#### Definition of hazards

31

### Hazards and glitches

#### Usual solutions

- wait until signals are stable by using a clock

- preferable

- easiest to design when there is a clock

- synchronous circuits

- design hazard-free circuits

- sometimes necessary

- asynchronous design

#### Static hazards

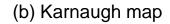

33  $f = x_1 x_2 + \overline{x}_1 x_3$  $f = x_1 x_2 + \overline{x}_1 x_3 + x_2 x_3$ *x*<sub>2</sub> р *X*<sub>1</sub> f q  $X_2$ X3 *X*1 (a) Circuit with a hazard X3 x3 00 01 11 10 0 1 (c) Hazard-free circuit (b) Karnaugh map hazard-free if more than one bit

of inputs change simultaneously?

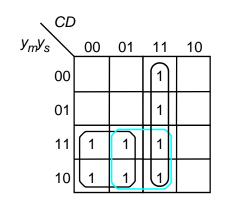

# Two-level implementation of master-slave D flip-flop

34

| Present | Next state                                           |        |

|---------|------------------------------------------------------|--------|

| state   | <i>CD</i> = 00 01 10 11                              | Output |

| Ym Ys   | Ym Ys                                                | Q      |

| 00      | 00 00 00 10                                          | 0      |

| 01      | 00 00 01 11                                          | 1      |

| 10      | 11 11 00 (10)                                        | 0      |

| 11      | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | 1      |

(a) Excitation table

$$Y_m = CD + \overline{C}y_m + Dy_m$$

$$Y_s = \overline{C}y_m + Cy_s + y_m y_s$$

(b) Karnaugh maps for  $Y_m$  and  $Y_s$  in Figure 9.6a

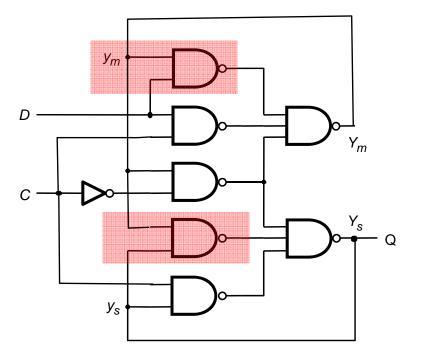

# Two-level implementation of master-slave D flip-flop (2)

(a) Minimum-cost circuit

(c) Hazard-free circuit

$$Y_m = CD + \overline{C}y_m + Dy_m$$

$$Y_s = \overline{C}y_m + Cy_s + y_m y_s$$

#### Static hazard in a POS circuit (0hazard)

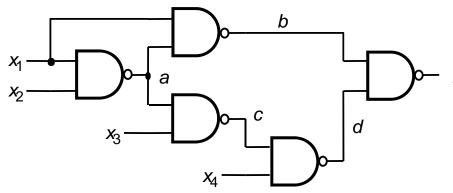

## dynamic hazards

#### 37

- there exist multiple paths for a given signal change to propagate along

- neither easy to detect nor easy to deal with

- using two-level hazard-free circuits

(a) Circuit

(b) Timing diagram

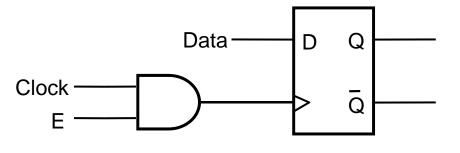

### CLOCK SYNCHRONIZATION (CHAPTER 10.3)

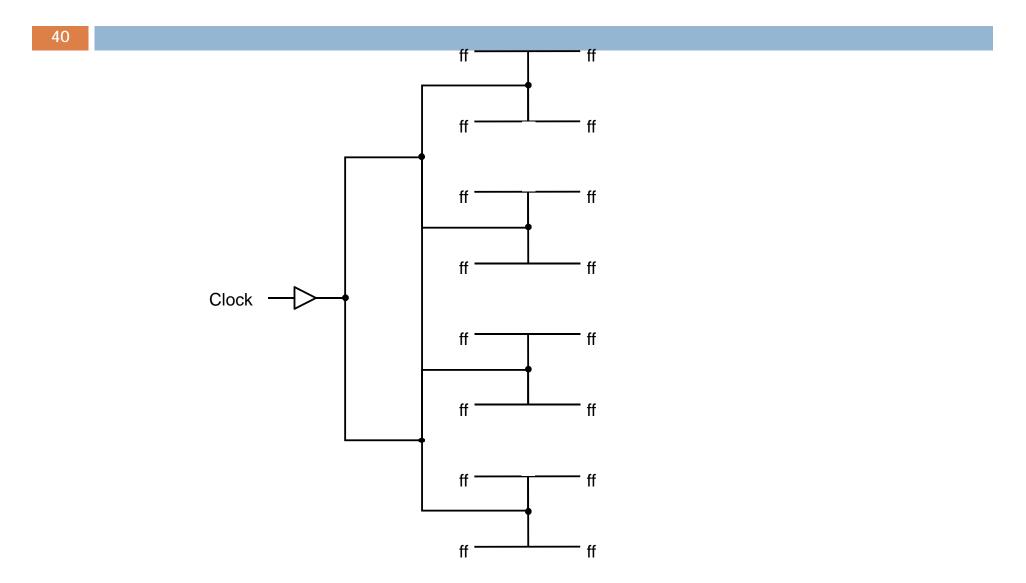

### Clock skew

39

#### the clock signal arrives at different times at different F/Fs

- with or without clock enable circuits

- wires whose lengths vary appreciably

#### An H-tree clock distribution network

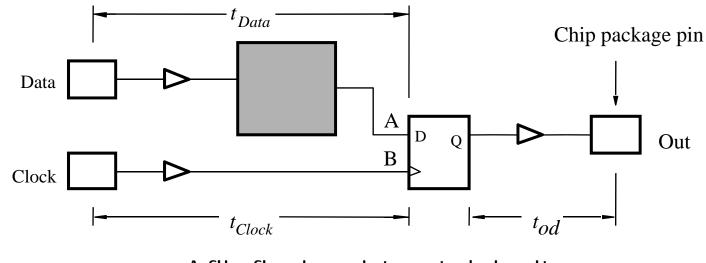

# F/F timing parameters

- $\Box$  setup time  $t_{su}$

- hold time  $t_h$

- **register delay or propagation delay**  $t_{rd}$

- output delay time t<sub>od</sub>

- required for the change in Q to propagate to an output pin on the chip

A flip-flop in an integrated circuit

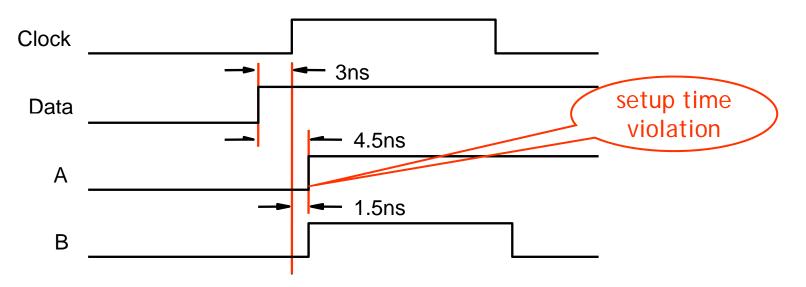

# F/F timing parameters, cont'd

- 42

- t<sub>co</sub> delay : active clock edge -> output change at an output pin

- $\bullet \quad t_{Clock} + t_{rd} + t_{od}$

- Example

- $t_{Clock} = 1.5ns, t_{rd} = 1ns, t_{od} = 2ns \rightarrow t_{co} = 4.5 ns$

- F/F timing in a chip

- t<sub>Clock</sub>=1.5 ns, t<sub>Data</sub>=4.5 ns, t<sub>su</sub>=3 ns

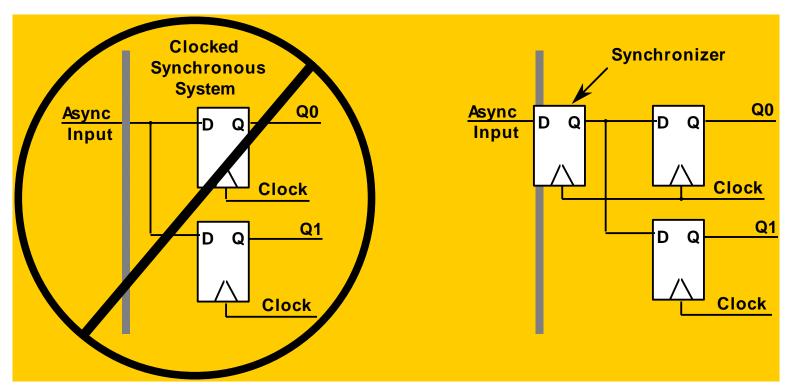

**Asynchronous Inputs Are Dangerous!**

Since they take effect immediately, glitches can be disastrous

Synchronous inputs are greatly preferred!

But sometimes, asynchronous inputs cannot be avoided e.g., reset signal, memory wait signal

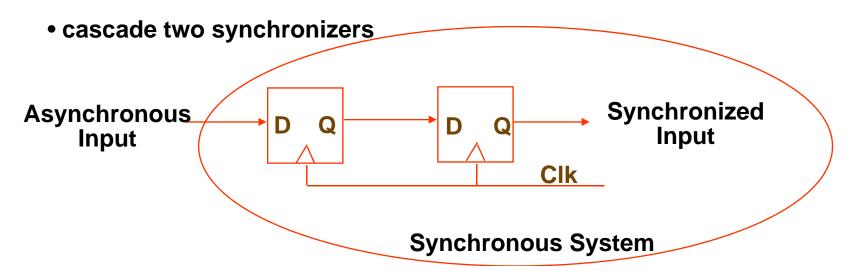

#### Handling Asynchronous Inputs

Never allow asynchronous inputs to be fanned out to more than one FF within the synchronous system

45

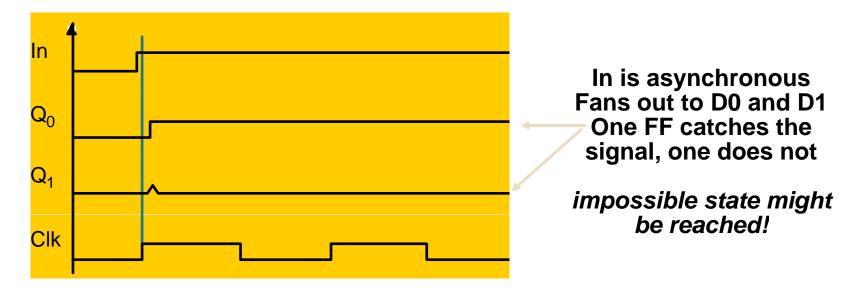

#### What Can Go Wrong

Single FF that receives the asynchronous signal is a synchronizer

46

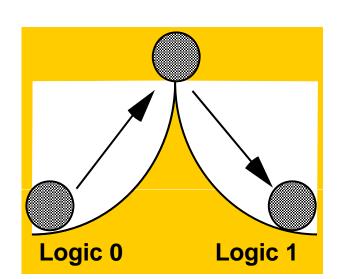

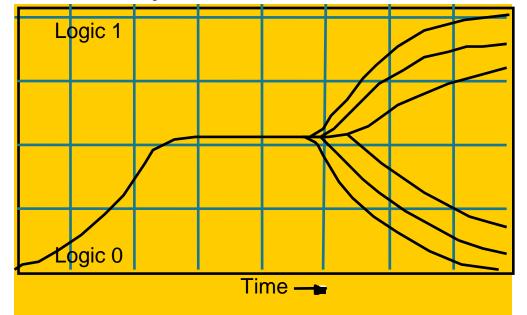

Synchronizer Failure

When FF input changes close to clock edge, the FF may enter the *metastable* state: neither a logic 0 nor a logic 1

It may stay in this state an indefinite amount of time, although this is not likely in real circuits

Small, but non-zero probability that the FF output will get stuck in an in-between state Oscilloscope Traces Demonstrating Synchronizer Failure and Eventual Decay to Steady State

Solutions to Synchronizer Failure

- the probability of failure can never be reduced to 0, but it can be reduced

- slow down the system clock this gives the synchronizer more time to decay into a steady state synchronizer failure becomes a big problem for very high speed systems

- use fastest possible logic in the synchronizer this makes for a very sharp "peak" upon which to balance S or AS TTL D-FFs are recommended

47